주기억장치에는 RAM과 ROM이 있다고 ep0에서 배웠다

우리가 지금까지 메모리라 불러왔던 RAM에 대해 더 자세하게 알아보자

ㅇRAM

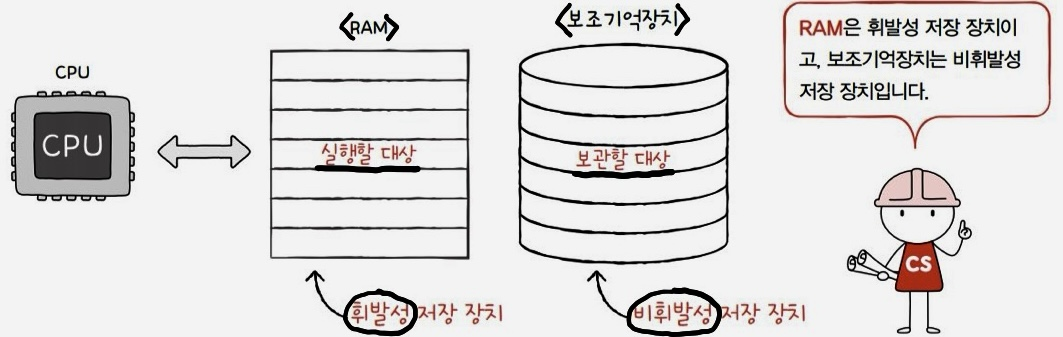

"메모리(RAM)에는 실행할 프로그램의 명령어 + 데이터가 저장된다"

(만약 CPU가 실행하고 싶은 프로그램이 보조기억장치에 있다면 이를 RAM으로 복사하여 저장한 뒤 실행)

휘발성(volatile): 전원을 끄면 저장된 내용이 사라진다 e.g. RAM

비휘발성(non- volatile): 전원을 커도 저장된 내용이 유지된다 e.g. 보조기억장치(HDD, SSD, CD-ROM, USB메모리 등), ROM

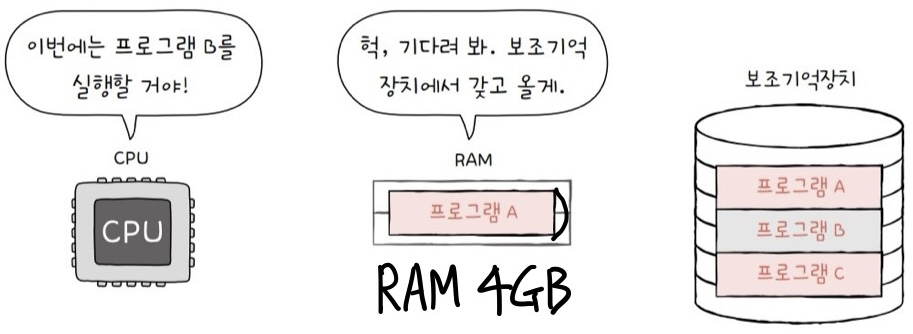

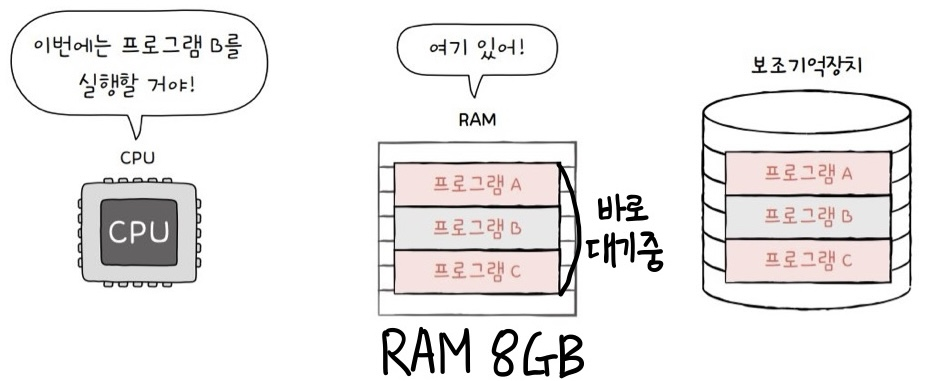

다다익램이란 말을 들어봤는가? 100%는 아니지만 어느 정도 맞는 말이다

램이 클 수록 많은 프로그램을 동시에 실행하는 데 유리하다

그렇다면 램의 종류에 대해 알아보자

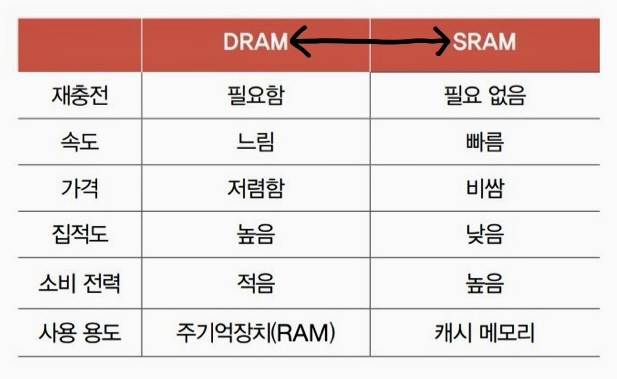

ㅇDRAM(Dynamic RAM): 저장된 데이터가 동적으로 사라진다

일반적으로 우리가 사용하는 램이다

커패시터에 전하를 충전하는 방식이기 때문에 데이터 소멸을 막기 위해 일정 주기로 재충전(재활성화)을 해줘야 한다

장점) 소비전력 ↓, 값이 싸다, 집적도 ↑

→ 대용량으로 설계하기 용이하다

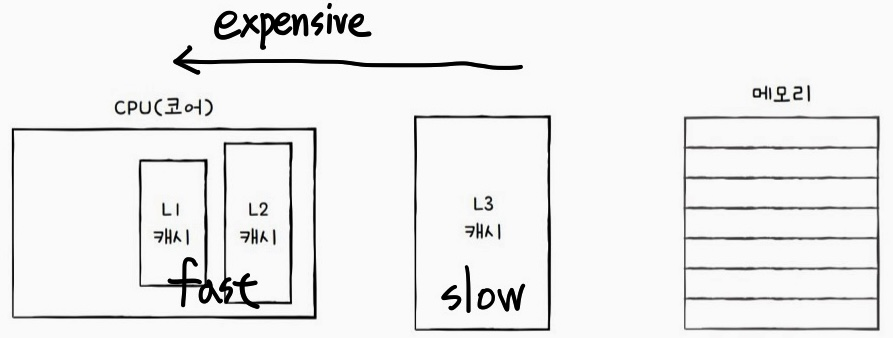

ㅇSRAM(Static RAM): 저장된 데이터가 변하지 않는다(하지만 전원 끄면 날라가는 건 동일하다)

이진값들이 플립-플롭(flip-flop) 논리 게이트를 이용하여 저장된다

보통 캐시 메모리로 사용된다

속도가 빠르며 주기적인 재충전(재활성화)이 필요없다

단점) 소비전력 ↑ , 값이 비싸다, 집적도 ↓

→ 대용량으로 설계하기 용이하지 않다

ㅇSDRAM(Synchronous DRAM): 클럭신호와 동기화된 DRAM

클럭 타이밍에 맞춰 CPU와 정보를 주고받음

==

클럭마다 CPU와 정보를 주고받을 수 있음

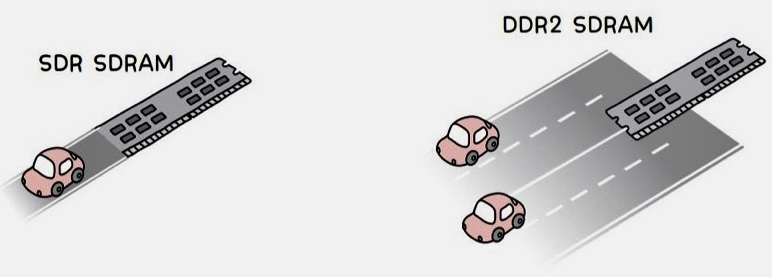

ㅇDDR SDRAM(Double Date Rate SDRAM): 대역폭을 두 배 넓혀 속도를 up 한 SDRAM

최근 가장 흔히 사용하는 DRAM

대역폭 = bandwidth = date rate

SDR SDRAM(Single Date Rate SDRAM): 한 클럭당 하나의 데이터

+

DDR2 SDRAM = DDR SDRAM x 2 = SDR SDRAM x 4

DDR3 SDRAM = SDR SDRAM x 8

DDR4 SDRAM = SDR SDRAM x 16 (요즘 시중의 램은 다 DDR4 SDRAM이다)

ㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡ

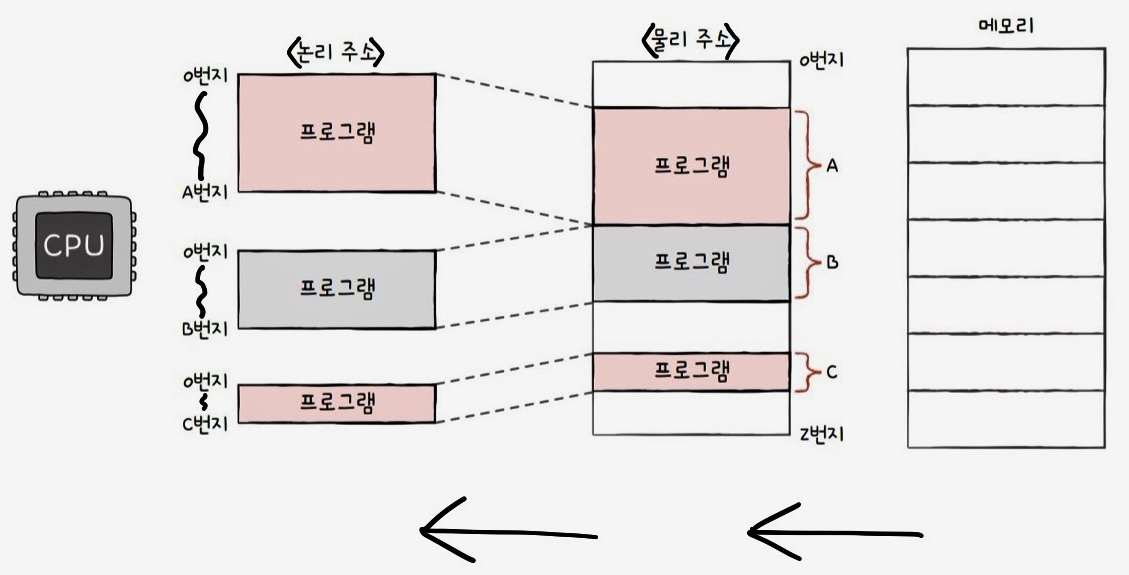

같은 프로그램을 실행하더라도 실행할 때마다 적재되는 주소는 달라진다

ㅇ물리주소: 하드웨어상의 주소

ㅇ논리주소: 실행 중인 프로그램 각각에 부여된 0번지부터 시작되는 주소

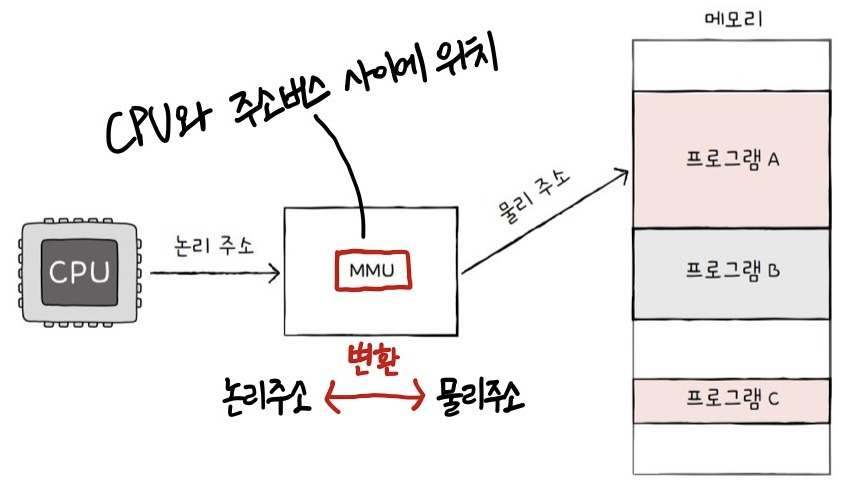

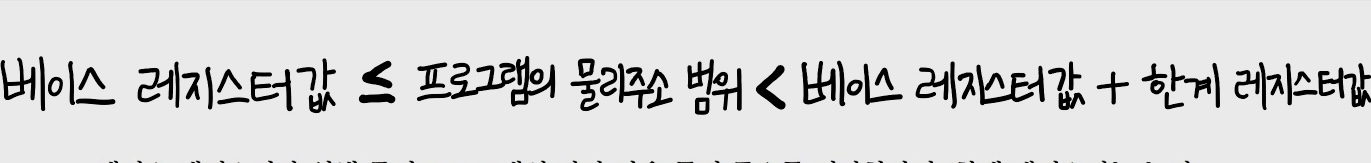

논리주소와 물리주소 간의 변환은 MMU가 맡는다

ㅇMMU(Memory Management Unit): 메모리 관리 장치

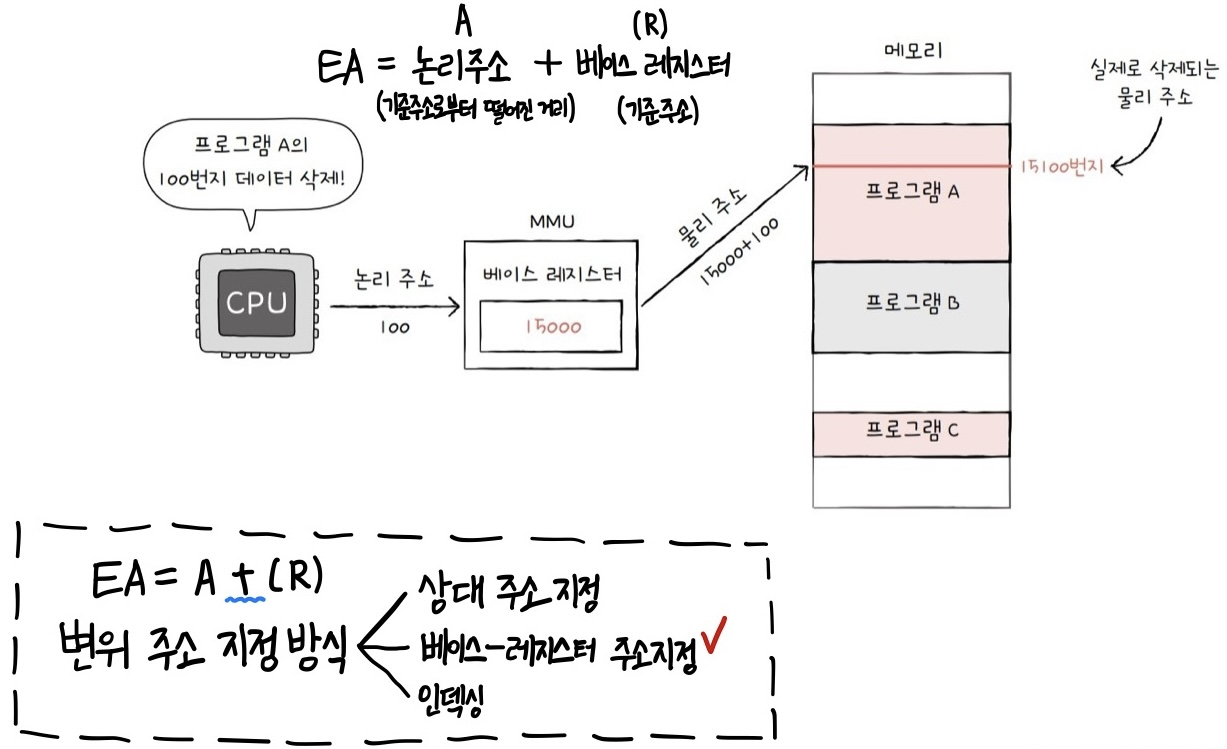

MMU가 논리주소를 물리주소로 변환하는 원리는 앞에서 배웠던

3가지 변위 주소 지정 방식 중 베이스-레지스터 주소 지정 방식이다

앞에서 배운 내용을 다시 상기해 보자

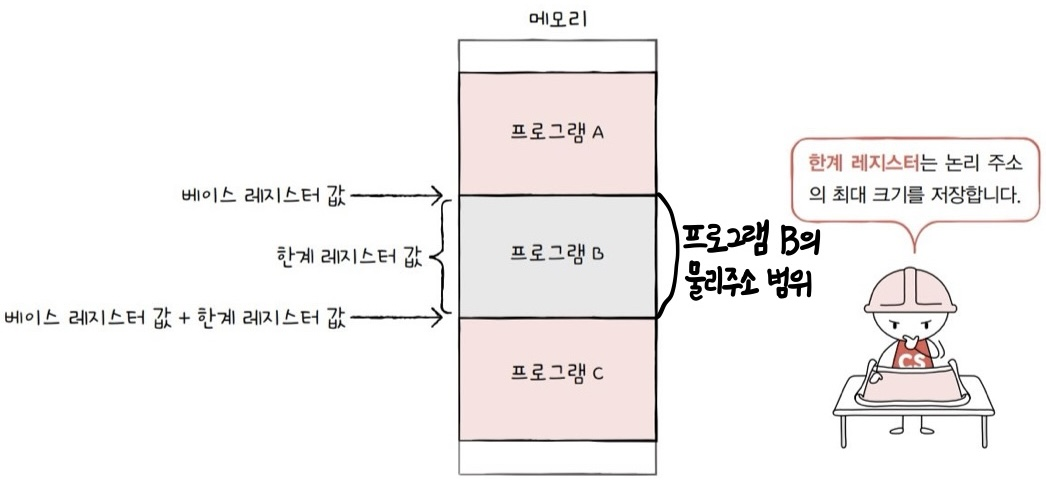

ㅇ메모리 보호 기법: 한계 레지스터가 담당(논리주소의 최대크기를 저장)

한계 레지스터(limit register): 논리주소의 최대크기를 저장해서 범위를 정해준다

<주소변환 플로우차트>

이러한 방식으로 실행 중인 프로그램의 독립적인 실행공간을 확보하고 하나의 프로그램이 다른 프로그램을 침범하지 못하게 보호한다

ㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡ

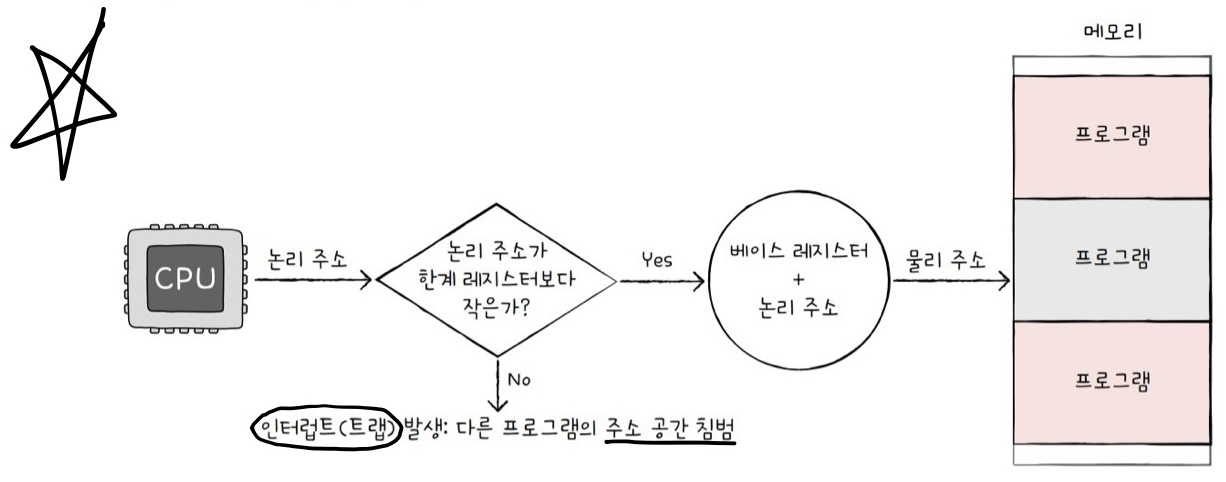

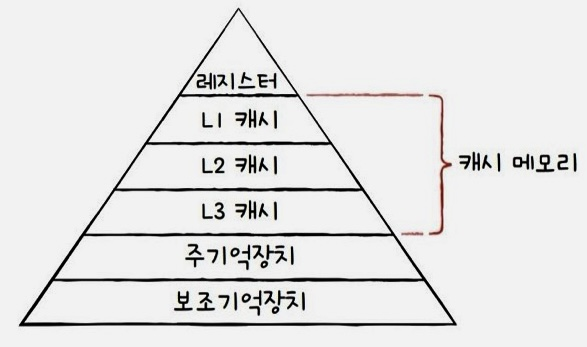

ㅇMemory Hierarchy(메모리 계층구조) - 여기서 말하는 메모리는 저장 장치이다

"메모리 계층구조를 통해 결과적으로 위쪽을 자주 접근하고 아래쪽을 덜 접근하여 전체적인 프로그램의 실행속도를 높인다"

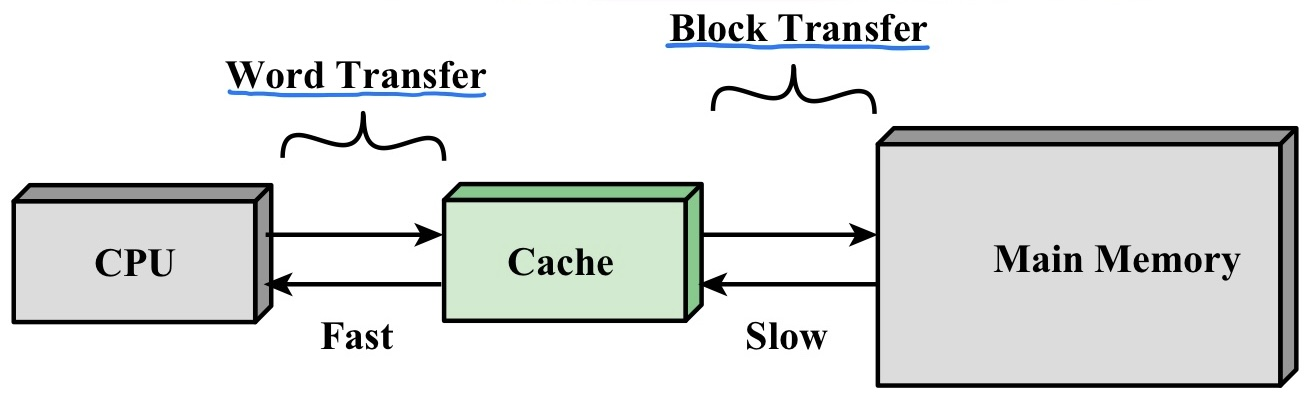

ㅇ캐시메모리(Cache memory)

CPU가 사용할 데이터를 미리 캐시메모리에 저장한 후 필요할 때 빠르게 사용한다

캐시메모리는 앞에서 배운 SRAM이며 CPU와 메모리 사이에 위치한다

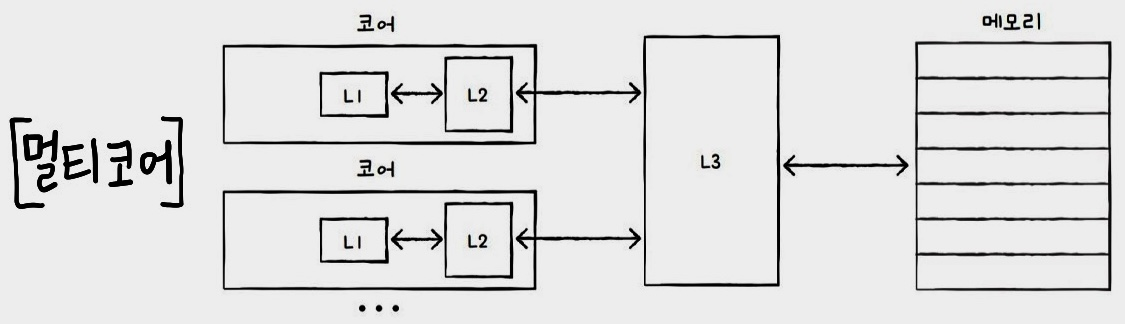

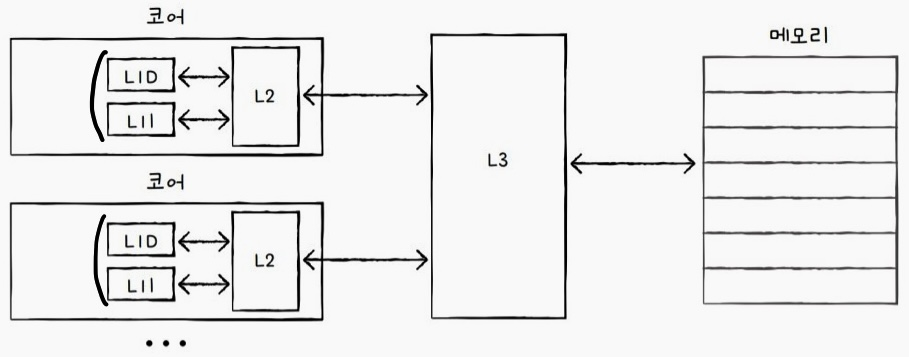

캐시는 계층적 캐시메모리 구조를 갖고 있다

일반적으로 L1 캐시와 L2 캐시는 코어 내부에 존재하고 L3 캐시는 코어 외부에 위치한다

멀티코어의 캐시그림을 보면 이해가 빠르다

그림과 같이 L1 캐시와 L2 캐시는 코어 내부에 고유하게 할당되고 L3 캐시는 여러 코어가 공유하는 형태로 코어 외부에 위치한다

+

분리형 캐시(Split Cache): L1 캐시를 두 개로 나눈다

그림과 같이 L1 캐시를 명령어만을 저장하는 L1캐시와 데이터만을 저장하는 L1캐시로 나눈 것이다

L1I 캐시: 명령어만을 저장

L1D 캐시: 데이터만을 저장

ㅇ참조 지역성 원리 - 2가지

캐시메모리는 CPU가 사용할 법한 대상을 예측하여 저장한다

이때 적중했을 때를 "캐시 히트", 적중 못했을 때를 "캐시 미스"라 한다

보통 컴퓨터의 캐시 적중률(cache hit ratio)은 85 ~ 95% 이상이다

여기서 캐시메모리는 참조 지역성의 원리 2가지를 따른다

1. CPU는 최근에 접근했던 메모리공간에 다시 접근하려는 경향이 있다

- 시간지역성: 최근에 접근했던 메모리공간에 다시 접근하려는 경향

2. CPU는 접근한 메모리공간 근처를 접근하려는 경향이 있다

- 공간지역성: 접근한 메모리공간 근처를 접근하려는 경향

Q. 캐시 관리를 OS가 하지 않는 이유는?

A. 캐시는 속도가 생명이기 때문에 빠른 액세스가 가능한 HW에서 관리한다

참고 및 출처: 컴퓨터시스템구조론(William Stallings), 혼공컴운(강민철), Operating Systems: Internals and Design Principles(William Stalling), Operating System Concepts(Silberschatz, Abraham)

'Computer Science > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] ep7) 보조기억장치 (1) | 2024.02.24 |

|---|---|

| [컴퓨터 구조] ep3) 컴퓨터 구조의 큰 그림 (1) | 2024.02.22 |

| [컴퓨터 구조] ep5) CPU 성능 향상 기법 (0) | 2024.02.14 |

| [컴퓨터 구조] ep4) CPU와 인터럽트 (3) | 2024.02.14 |

| [컴퓨터 구조] ep2) 명령어와 주소 지정 방식 (2) | 2024.02.11 |