세계 곳곳의 과학자들과 엔지니어들은 조금이라도 더 빠른 CPU를 만들기 위해 혈색이다

이번 장에서는 CPU 설계 기법과 명령어 처리 기법들에 대해 알아보겠다

ㅇ클럭

"컴퓨터 부품들은 클럭이라는 박자에 맞춰 작동한다"

클럭속도는 헤르츠(Hz) 단위로 측정되며 클럭속도가 곧 CPU속도이다

클럭속도에는 기본클럭속도(Base)와 최대클럽속도(Max)가 있다 CPU는 계속 일정한 클럭속도를 유지하기보다는 고성능을 요하는 순간에 순간적으로 클럭속도를 높이고 그렇지 않은 순간에는 클럭속도를 낮춘다

여기서 최대 클럭속도를 강제로 더 끌어올릴 수가 있는데 이런 기법을 오버클럭킹이라 한다

(+ 그렇다고 해서 무턱대고 클럭속도를 높이기만 하면 안된다, 발열문제는 늘 우리를 따라다니는 숙적같은 존재이다)

ㅇ코어

CPU가 과거에는 하나만 있었지만 요즘에는 기술이 발달해 여러 개의 CPU를 한 개의 장치에 탑재해서 사용한다

이때 각각의 CPU를 우리는 코어라고 부른다

여기서 우리는 코어를 여러 개 포함하고 있는 CPU를 멀티코어 CPU 또는 멀티코어 프로세서라고 부른다

+

역시 연산처리 속도가 꼭 코어 수에 비례해서 증가하는 건 아니다

4개의 라멘을 10명의 요리사가 만드는 게 6명의 요리사가 만드는 것보다 특별히 더 빠르지 않은 느낌이다

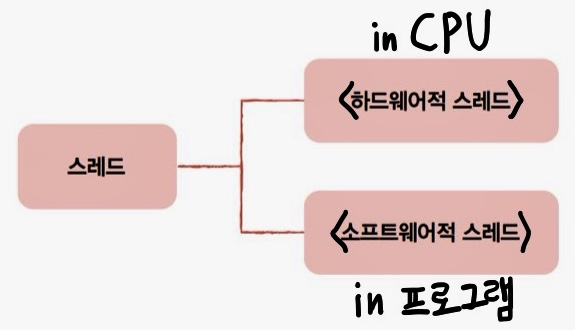

ㅇ스레드: 실행 흐름의 단위

스레드는 개념을 정확히 짚고 넘어가야 한다

스레드는 하드웨어적 스레드일 때와 소프트웨어적 스레드일 때의 의미가 다르다

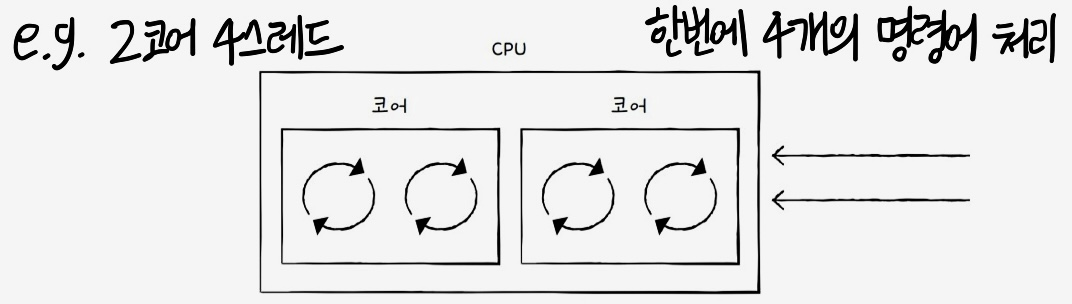

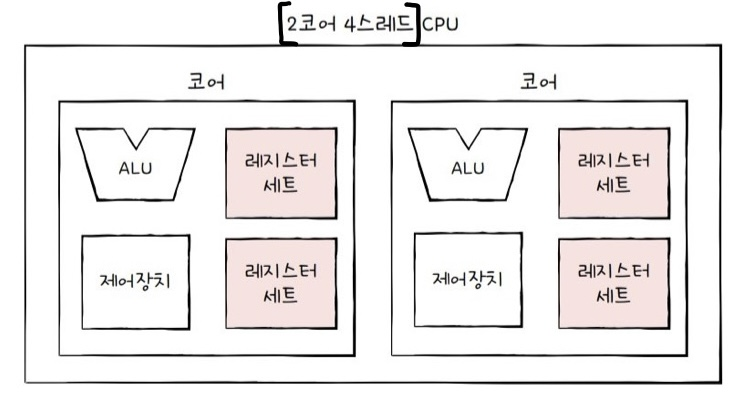

<하드웨어적 스레드>: 하나의 코어가 동시에 처리하는 명령어 단위

그림과 같이 2코어 4스레드인 경우에는 한 번에 4개의 명령어 처리가 가능하다

이처럼 하나의 코어로 여러 명령어를 동시에 처리하는 CPU를 멀티스레드 CPU 또는 멀티스레드 프로세서라 한다

추가) 하이퍼스레딩은 intel에서 밀고있는 멀티스레딩 기술이다

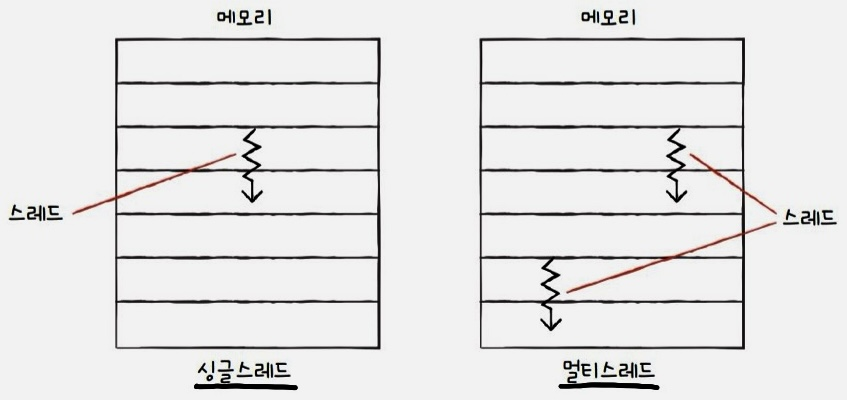

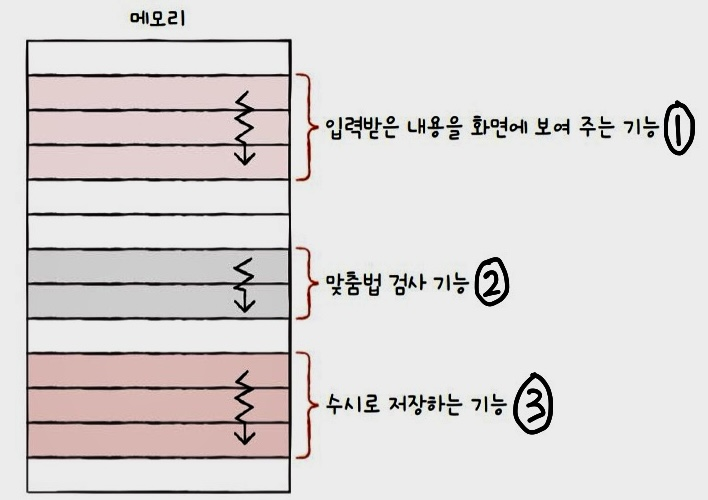

<소프트웨어적 스레드>: 하나의 프로그램에서 독립적으로 실행하는 단위

가령 우리가 아래의 기능들이 동시에 수행되길 원한다고 해보자

1. 사용자로부터 입력받은 내용을 화면에 보여주는 기능

2. 사용자가 입력한 내용이 맞춤법에 맞는지 검사하는 기능

3. 사용자가 입력한 내용을 수시로 저장하는 기능

이 기능들을 작동시키는 코드를 각각의 스레드로 만들면 동시에 실행할 수 있다 (Python, Java, C++ 등의 언어로)

더 자세한 건 운영체제에서 배운다

우리는 지금 운영체제가 아닌 컴퓨터 구조를 배우고 있으므로 소프트웨어적 스레드가 아닌 하드웨어적 스레드에 집중하겠다, 멀티스레드 프로세서의 가장 큰 핵심은 레지스터이다

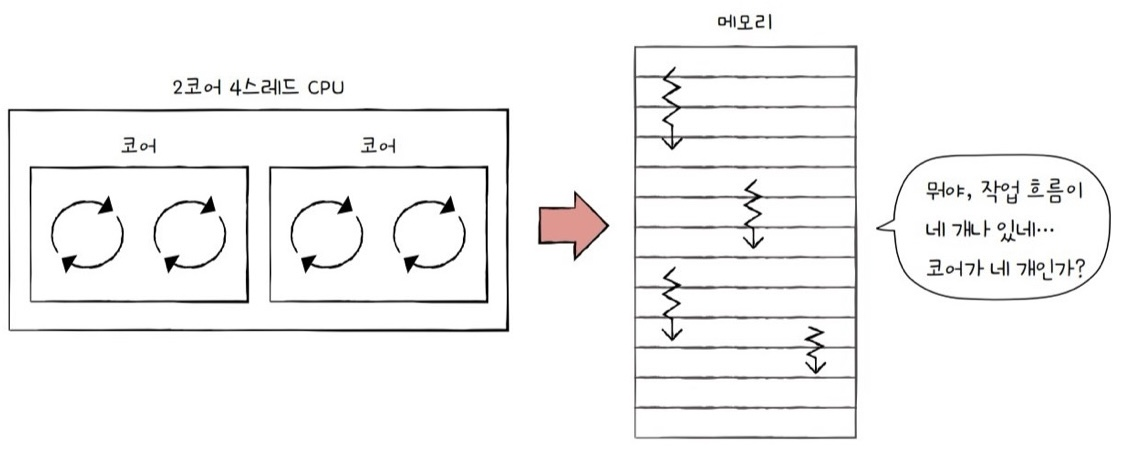

메모리 속 프로그램 입장에서 봤을 때 하드웨어 스레드는 마치 '한 번에 하나의 명령어를 처리하는 CPU'처럼 보인다

가령 2코어 4스레드 CPU는 한 번에 하나의 명령어를 처리하는 CPU가 4개가 있는 것처럼 보이기 때문에 하드웨어 스레드를 논리 프로세서라고 부르기도 한다

정리)

코어: 명령어를 실행할 수 있는 '하드웨어 부품'

스레드: 명령어를 실행하는 '단위'

멀티코어 프로세서: 명령어를 실행할 수 있는 하드웨어 부품이 CPU 안에 두 개 이상 있는 CPU

멀티스레드 프로세서: 하나의 코어로 여러 개의 명령어를 동시에 실행할 수 있는 CPU

ㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡ

명령어 병렬 처리 기법의 3가지를 살펴보자

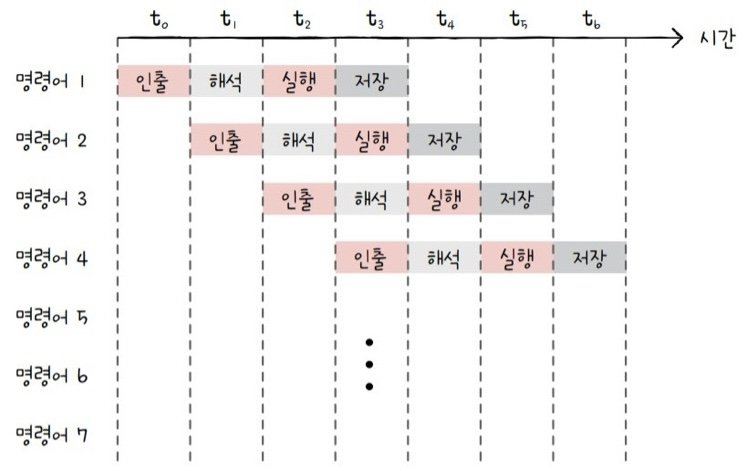

명령어 처리 과정을 클럭단위로 나누어 보면 다음 순서와 같이 나눌 수 있다

1. 명령어 인출

2. 명령어 해석

3. 명령어 실행

4. 결과 저장

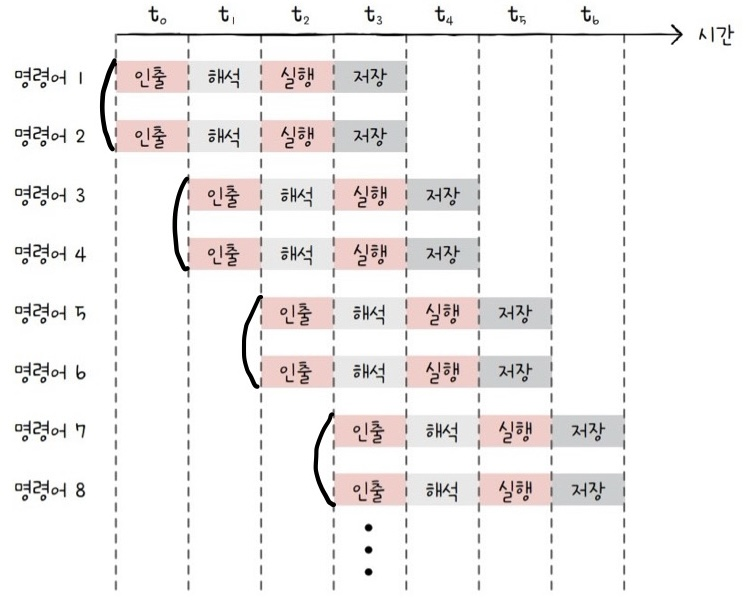

ㅇ 명령어 파이프라이닝: 동시에 여러 개의 명령어를 겹쳐서 실행

그림과 같이 순서대로 동시에 진행시킨다 (포드의 자동차 공장을 생각하자)

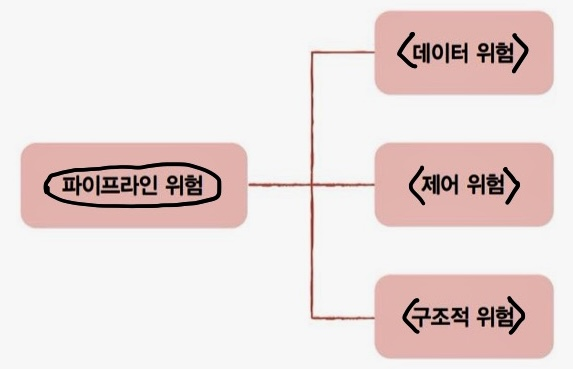

하지만 파이프라인은 특정 상황에서 성능 향상에 실패하는 경우도 있다

이를 파이프라인 위험이라 부르고 크게 <데이터 위험>, <제어 위험>, <구조적 위험> 3가지로 나눈다

<데이터 위험>: 명령어 간 '데이터 의존성'에 의해 발생

명령어 1: R1 <- R2 + R3 // R2 레지스터 값과 R3 레지스터 값을 더한 값을 R1 레지스터에 저장

명령어 2: R4 <- R1 + R5 // R1 레지스터 값과 R5 레지스터 값을 더한 값을 R4 레지스터에 저장

이런 경우에는 명령어 1이 끝나야지만 다음 명령어 2가 진행이 된다 따라서 무턱대고 동시에 실행시킬 수가 없다

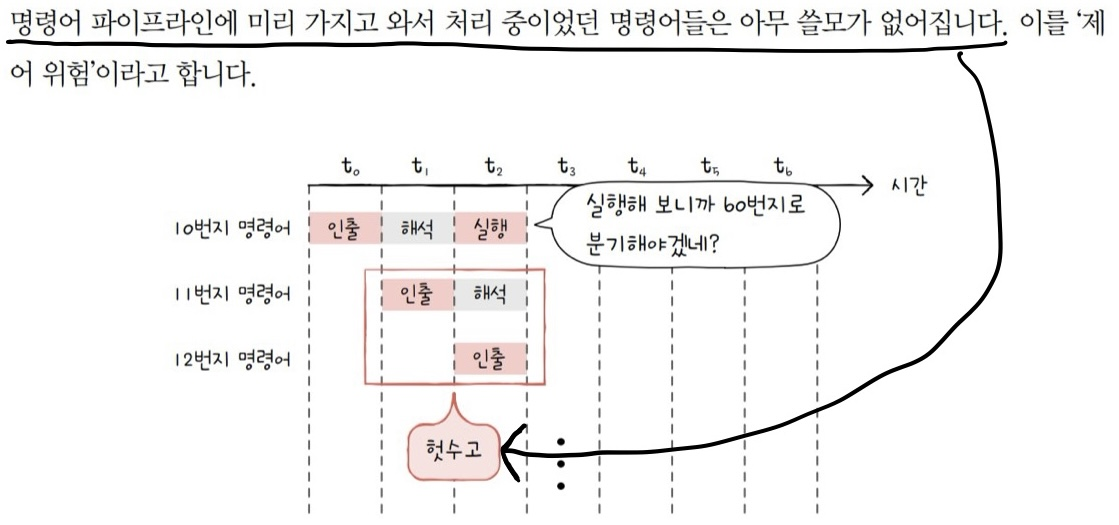

<제어 위험>: 주로 분기 등으로 인한 PC(프로그램 카운터)값의 갑작스러운 변화에 의해 발생

e.g. jump 명령어, call 명령어

<구조적 위험>: 서로 다른 명령어가 동시에 ALU, 레지스터와 같은 CPU 부품을 사용하려 할 때 발생

자원 위험 이라고도 한다

ㅇ슈퍼스칼라: 여러개의 파이프라인을 이용(파이프라인의 다중화)

오늘날의 멀티스레드 프로세서이다

(여러 개의 파이프라인을 이용하면 속도는 빨라지지만 위험도 커진다)

ㅇ비순차적 명령어 처리(OoOE): 명령어들을 순차적으로 실행하지 않는 기법(합법적인 새치기)

Out-of-Order Execution

순서를 바꿔 실행해도 무방한 명령어를 먼저 실행하여 명령어 파이프라인이 멈추는 것을 방지하는 기법

ㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡ

ㅇISA(Instruction Set Architecture): 명령어 세트

CPU가 이해할 수 있는 명령어들의 집합이다

"ISA는 CPU의 언어이자 HW가 SW를 어떻게 이해할지에 대한 약속이다"

(명령어 집합에 '구조'라는 단어가 붙은 이유는 CPU가 어떤 명령어를 이해하는지에 따라서 컴퓨터 구조 및 설계 방식이 달라지기 때문이다)

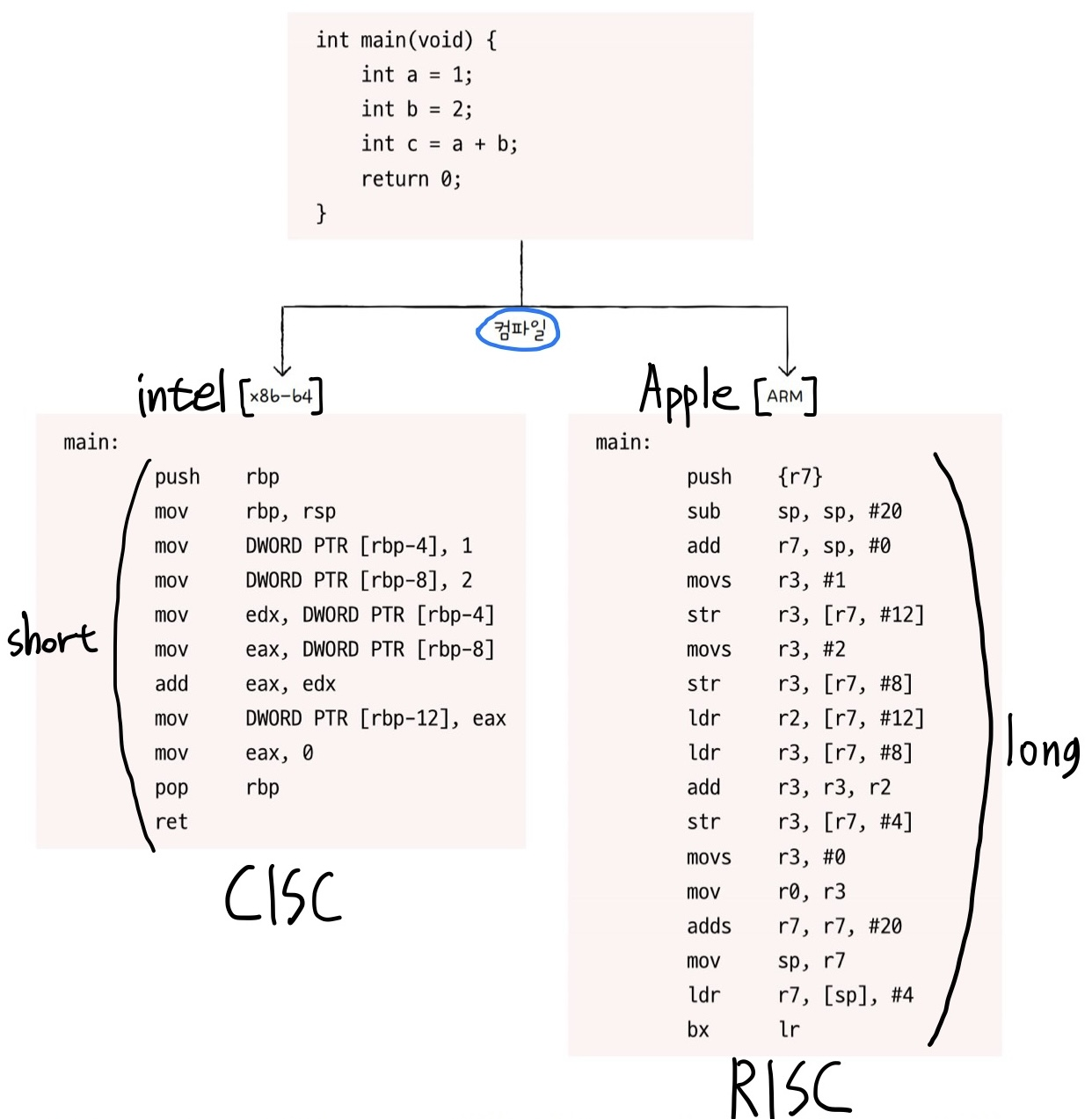

e.g. intel의 x86(32bit) ISA / x86-64(64bit) ISA, 애플의 아이폰 속 CPU ARM ISA

동일한 소스 코드를 작성하고 ISA가 다른 컴퓨터에서 어셈블리어로 컴파일하면 위와 같은 결과를 얻을 수 있다

(사용한 컴파일러에 따라서도 어셈블리어가 달라질 수는 있다, 위 예시에서는 gcc 11.2라는 동일한 컴파일러를 사용하였다)

ㅇCISC: Complex Instruction Set Computer (복합 명령어세트 컴퓨터)

앞서 말한 intel의 x86(32bit) ISA / x86-64(64bit) ISA가 대표적인 CISC 기반의 ISA이다

위 그림을 보면 CISC는 RISC에 비해 명령어가 짧은 것을 알 수가 있다, CISC는 가변 길이 명령어를 활용한다

Pros: 적은 수의 명령으로 메모리 절약

Cons: 명령어의 규격화가 어려움 -> 파이프라이닝 hard

명령어들의 사용 빈도가 낮다

ㅇRISC: Reduced Instruction Set Computer (축소 명령어세트 컴퓨터)

앞서 말한 ARM이 대표적인 RISC 기반의 ISA이다

위 그림을 보면 RISC가 CISC에 비해 명령어가 긴 것을 알 수가 있다, RISC는 고정 길이 명령어를 활용한다

RISC는 CISC와 상반된다 생각하면 된다

.

.

.

+ intel과 ARM 추가지식)

응용 프로세서: 우리가 지금까지 배운 일반적인 프로세서 e.g. intel processor

전용 프로세서: 임베디드 시스템 전용으로 크기와 가격을 줄이도록 설계 e.g. ARM

ARM제품들은 보통 임베디드에서 많이 쓰인다

임베디드 시스템은 그 목적으로만 만들어 자체제작을 값싸게 한다(저전력/저가) e.g. 가전, 자동차, 비행기

<대표적인 ARM 제품들 리스트>

CORTEX-A / CORTEX-A50: 전자장치 프로세서 e.g. 세탁기, 휴대폰

CORTEX-R: 실시간 처리 프로세서 e.g. 센서 (R이 real-time의 r이다 - 믹싱에서 waves사의 real-time 오토튠 플러그인을 생각하자)

CORTEX-M: 제어전용 및 저전력 프로세서

참고 및 출처: 컴퓨터시스템구조론(William Stallings), 혼공컴운(강민철)

'Computer Science > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] ep3) 컴퓨터 구조의 큰 그림 (1) | 2024.02.22 |

|---|---|

| [컴퓨터 구조] ep6) 메모리와 캐시메모리 (0) | 2024.02.19 |

| [컴퓨터 구조] ep4) CPU와 인터럽트 (3) | 2024.02.14 |

| [컴퓨터 구조] ep2) 명령어와 주소 지정 방식 (2) | 2024.02.11 |

| [컴퓨터 구조] ep1) 데이터 (1) | 2024.02.10 |